Negli invertitori realizzati con il transistore MOS, si è potuto osservare che nessuno di questi avesse un consumo di potenza statica nullo. Inoltre, non veniva mai raggiunto in uscita il valore basso o alto totale (rispettivamente 0 e VDD).

L’invertitore nMOS a carico resistivo porta in uscita l’alimentazione tutta con ingresso basso, mentre un invertitore pMOS a carico resistivo porta in uscita uno zero se l’ingresso è pari all’alimentazione. In queste condizioni, il consumo di potenza è nullo per entrambi (nMOS e pMOS sono spenti nelle condizioni definite, la corrente di drain é nulla). Si pensi allora di unire queste due caratteristiche in un unico circuito.

Come mostrato in figura 1, il circuito è formato da una coppia di transistori MOS, un nMOS a pull-down e un pMOS a pull-up, creando così una simmetria complementare tra pull-up e pull-down. Questo circuito, per le caratteristiche definite, è chiamato invertitore CMOS (MOS complementare).

|

| Figura 1: invertitore CMOS |

I due transistori sono caratterizzati dallo stesso beta e dalla stessa tensione di soglia. Le leggi che governano il circuito sono le seguenti:

Le regioni di funzionamento, in base alle disequazioni caratteristiche, sono:

in figura 2, vi è il grafico preliminare che mostra le regioni di funzionamento dell'invertitore CMOS, fatta a priori dell'analisi alle correnti.

|

| Figura 2: regioni di funzionamento di un invertitore CMOS. |

- Mn OFF, Mp LIN: la rete di pull-down è spenta, ma è accesa solo la rete di pull-up. Dal grafico in figura 3, è la regione in rosso chiaro a destra.

- Mn LIN, Mp OFF: al contrario del caso precedente, la rete di pull down è accesa e quella di pull-up spenta, zona arancione in figura 2. Comunque, essendoci un transistore spento, il pMOS, la corrente deve essere identicamente nulla:

- Mn SAT, Mp LIN: la tensione di ingresso supera la tensione di soglia e si accende il transistore nMOS a pull-down (regione in azzurro figura 2):

.png)

raffigura un arco di parabola con concavità verso il basso e centrato in VT;

- Mn SAT, Mp SAT: regione in giallo al centro del grafico. Non essendo una funzione della tensione di uscita, si ricava l'esatto valore di tensione in ingresso per il quale entrambi lavorano in saturazione:se ci si trovasse di fronte a due transistori completamente differenti, allora questo punto diventa funzione di tutti i parametri:dipende dai fattori di forma (W e L per intendersi)

- Mn LIN, Mp SAT è il caso opposto in cui i transistori si cambiano la regione di funzionamento (regione in verde). L'equazione dell'uscita diviene:

Il grafico finale della caratteristica ingresso uscita è raffigurato in figura 3:

|

| Figura 3: caratteristica statica di un invertitore CMOS. |

Subito si nota una caratteristica differente da tutti gli altri invertitori che utilizzavano uno o due transistori MOS: il valore basso è pienamente zero, il valore alto è l'alimentazione. Assegnando all'ingresso il valore basso, si ottiene in uscita il valore alto pieno e viceversa.

Dalla caratteristica si possono notare questi due punti. Inoltre,

quando l'ingresso è basso la corrente che circola è nulla (pull-down OFF) e, allo stesso modo, anche quando l'ingresso è alto la corrente è nulla (pull-up OFF).Da queste considerazioni, infatti, il calcolo della potenza in questi due istanti è completamente nullo! Quindi, l'invertitore CMOS risolve il problema del consumo di potenza statica e per questa ragione viene definito ratioless.

Il grafico in figura 4 mostra la caratteristica corrente tensione dell'invertitore CMOS. LA corrente di drain è erogata solo quando uno dei due/entrambi i transistori lavora/lavorano in regione di saturazione.

|

| Figura 4: corrente di drain in funzione della tensione applicata sull'ingresso. |

Porte logiche in CMOS

Per la potenza statica nulla e per la vasta integrazione dei transistori mos nei circuiti integrati, la logica CMOS è fortemente diffusa nei circuiti digitali. L'invertitore è soltanto la prima porta logica realizzabile in CMOS. Possono essere realizzare, infatti, tutte le logiche negate possibili e immaginabili, progettando adeguatamente la posizione dei transistori nelle reti di pull-up e pull-down.

Prima di tutto, occorre ricordare che il transistore lavora, in regime digitale, come un interruttore che assume valore basso (ON) e valore alto (OFF) e viene controllato da un segnale di ingresso in tensione sul gate.

La porta NOR, ad esempio, è la somma negata di due (o più) variabili digitali. Assume il valore basso

Y = 0 se le variabili che compaiono al proprio interno assumono valore 1:

assumere in uscita valore zero significa avere due interruttori chiusi, in parallelo, che colleghino l'uscita alla massa, dunque da collocare nella rete di pull-down. Per questo si usa una coppia si nMOS in parallelo, come mostrato in figura 5.

|

| Figura 5: rete di pull-down per la porta NOR. |

con lo stesso ragionamento, ora, si vuole capire quando assume valore

Y=1:entrambi (sia uno sia l'altro) gli ingressi devono essere spenti per avere un'uscita pari al valore alto. Sono quindi necessari due interruttori controllati, collegati in serie, che colleghino l'uscita al valore dell'alimentazione quando il segnale di controllo è nullo, quindi un pMOS (figura 6).

|

| Figura 6: rete di pull-up per porta NOR. |

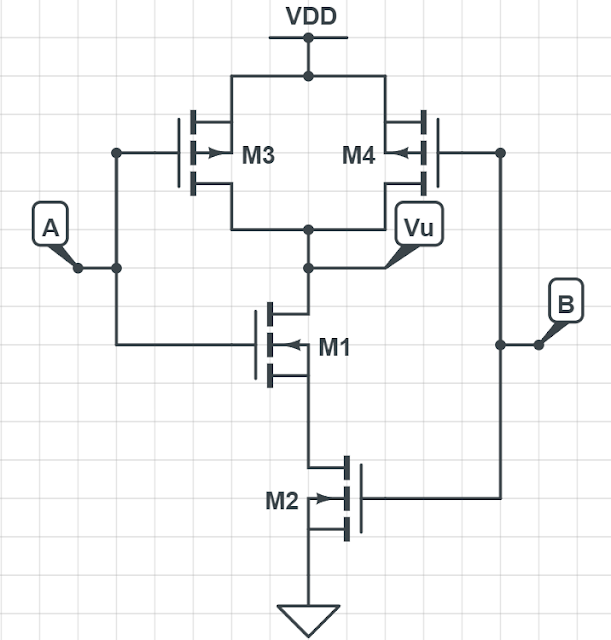

Collegando insieme le due reti appena progettate, si ottiene la porta NOR completa in logica CMOS, mostrata in figura 7:

|

| Figura 7: porta NOR in CMOS. |

La creazione di porte logiche in logica CMOS segue una regola precisa:

- Il prodotto di n variabili si riflette in una serie di n transistori nMOS nella rete di pull-down e un parallelo di n transistori pMOS nella rete di pull-up;

- la somma di n variabili si riflette in un parallelo di n transistori nMOS nella rete di pull-down e in una serie di n transistori pMOS nella rete di pull-up.

Le porte logiche non negate come l'AND o l'OR possono essere realizzate si in CMOS, ma con il collegamento sull'uscita di un semplice invertitore.

La porta NAND, invece, è il prodotto negato di due (o più) variabili. Assume valore basso quando entrambe le variabili sono al valore alto:

si devono dunque avere due transistori nMOS in serie che collegano l'uscita a massa quando sono accesi entrambi, come mostrato in figura 8:

|

| Figura 8: rete di pull-down della porta NAND. |

La stessa porta logica assume valore alto se uno dei due ingressi assume valore 1:

questo significa che sono necessari due transistori che colleghino all'alimentazione quando uno o l'altro sono accesi. Bastano due pMOS in parallelo alla rete di pull-up. Si osservi la figura 9

|

| Figura 9: rete di pull-up della porta NOR. |

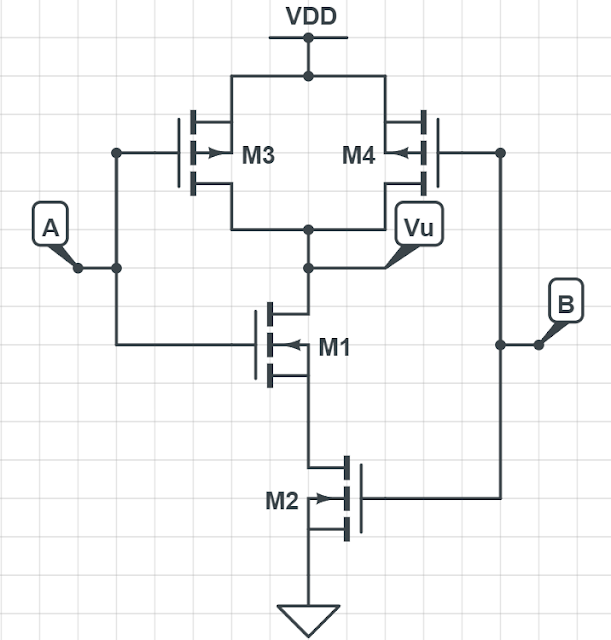

La porta NOR totale viene (figura 10):

|

| Figura 10: porta NAND in CMOS. |

In conclusione,

la realizzazione di una porta logica con n ingressi prevede che siano utilizzati 2n transistori MOS. Il progettista elettronico deve tenere conto di questi parametri, assieme alle dimensioni geometriche dei transistori, per un’ottimizzazione dell’occupazione d’area.

.png)

.png)

.png)

.png)

.png)

.png)

.png)

.png)

.png)

.png)

Commenti

Posta un commento