Il sommatore binario, dall’ half-adder al full-adder

Se in regime analogico si fa uso di un’amplificatore operazionale e alcune resistenze per eseguire la somma di segnali, in regime digitale esiste un vero e proprio blocco logico che svolge la somma di bit: il full-adder, indicato FA.

Half Adder

La somma, come nell'aritmetica decimane (studiata fin dalle elementari) prevede che due numeri sommati possano dare una somma S e un riporto C. Scelti due bit ai e bi, la somma si e il riporto ci sono ottenuti come mostrato in tabella 1:

|

| Tabella 1: tabella della verità di somma e riporto. |

Osservando la tabella, si nota dubito che la somma binaria è identicamente uguale alla funzione logica XOR (l'uscita va a 1 se soltanto uno dei due ingressi è a 1) e il riporto è identicamente uguale alla funzione logica AND. In figura 1 è mostrato lo schema logico di un Half-adder.

|

| Figura 1: blocco half-adder. |

Full-adder (FA)

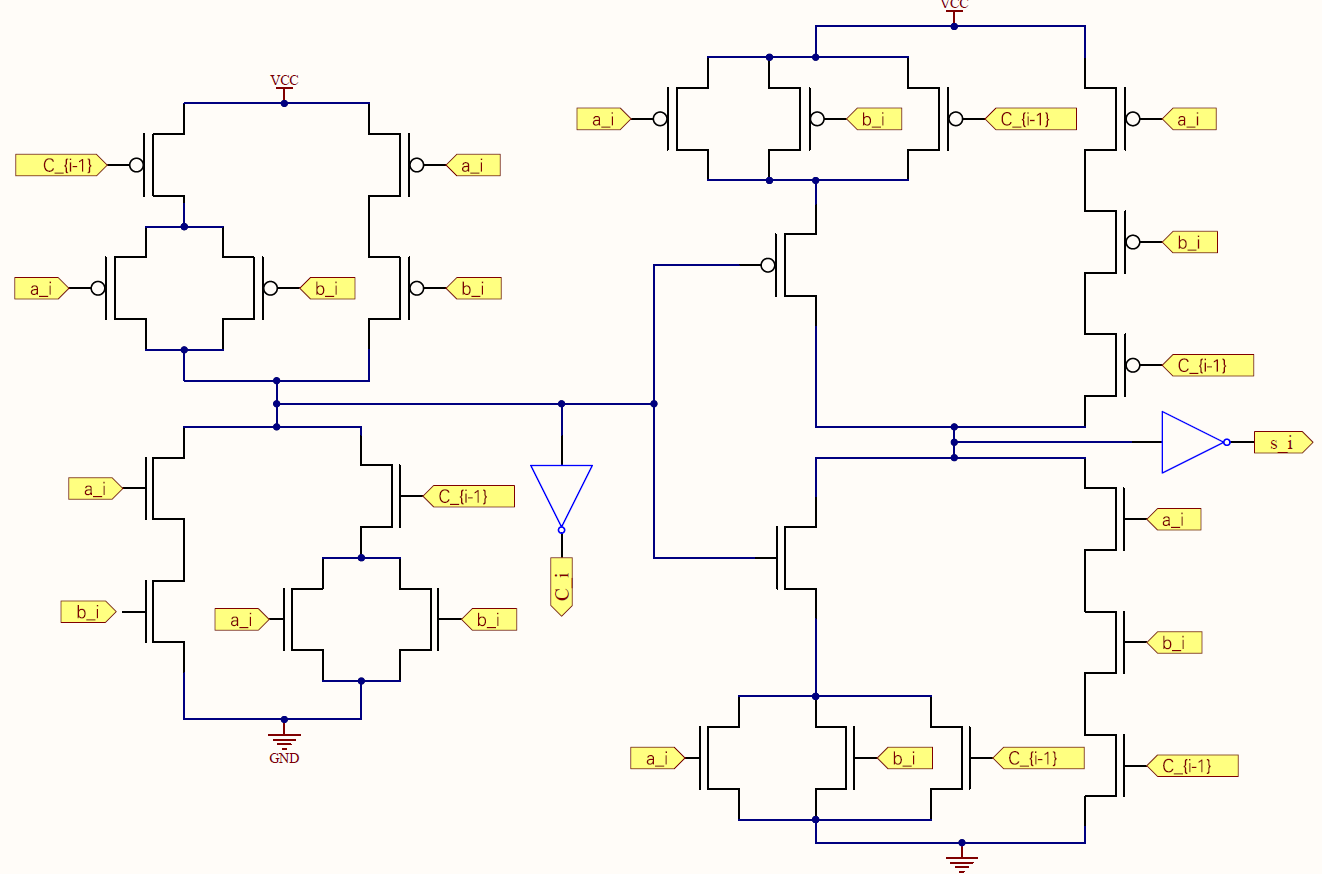

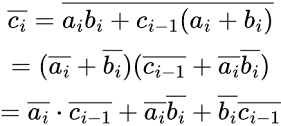

In figura 2 vi è lo schema logico che rappresenta tramite blocchi AND, OR e XOR. Viste le considerazioni sui vantaggi della tecnologia CMOS, si cerca di realizzare tutte le funzioni con la suddetta logica. Nella funzione del riporto, lo XOR logico tra i bit ai e bi può essere calcolato con un OR. Questo è possibile in quanto è il risultato di una medesima mappa K, con un diverso raggruppamento.

|

| Figura 2: schema logico del full-adder. |

Il circuito logico mostra chiaramente che la composizione interna di un full-adder è fatta di una coppia di half-adder e un OR logico. Si possono fare subito due considerazioni:

- L’area occupata da un full-adder supera il doppio dell’area occupata da un half-adder, proprio per il fatto di avere al proprio interno due half-adder e un OR;

- Il tempo di propagazione valutato sul percorso critico, quello per il quale il segnale attraversa più porte logiche, è ovviamente maggiore. In un half-adder un segnale può attraversare al più una porta logica. Nel full-adder, un percorso critico potrebbe essere quello del segnale ai, che attraversa XOR1, AND2 e OR1.

- 4 + 2 = 6 MOS per la porta AND. Essendoci due porte AND, si ha un totale di 12 MOS;

- 4 + 2 = 6 MOS per la porta OR, che è singola;

- 4 MOS per la porta NAND, presa tre volte, quindi 12 MOS, più i 4 per le porte NOT. Dunque 16 MOS per la porta XOR. Essendo presenti due XOR, si ha un totale di 32 MOS.

|

| Figura 3: rete CMOS del riporto. |

Valutazione dei tempi di propagazione

- rete del riporto: il caso peggiore per la rete di pull-down si ottiene quando sono accesi in serie ai e bi, mentre è spento ci-1. Il valore del beta equivalente è:

Per la rete di pull-up allo stesso modo il beta equivalente di caso peggiore è ottenuto quando sono accesi gli stessi MOS, con la differenza che si ha la serie di due pMOS in serie e una coppia in parallelo. Il beta equivalente è: - rete della somma: il pull-down porta a un caso peggiore quando sono accesi in serie ai e bi e ci-1. Essendo tre MOS in serie, il beta equivalente è: Tenendo sempre accesi i tre ingressi appena definiti, la rete di pull-up vede tre pMOS in serie a un parallelo di 3 pMOS. Il beta equivalente in questo caso è:

|

| Figura 5: rete di riporto in CMOS, seconda versione. |

La particolarità di questa rete è che, rispetto alla figura 4, la posizione dei pMOS nel pull-up del caso precedente è ora assunta dagli nMOS nel pull-down. Si è verificata una sorta di scambio tra le due reti di riporto.

Con ciò, il beta equivalente del pull-up è uguale al beta equivalente della rete di pull-down del caso precedente. Ugualmente per il pull-down.

In virtù di queste considerazioni, è possibile asportare le due reti con beta equivalente minore, e costruire una rete di riporto con architettura speculare, in cui la posizione relativa dei transistori MOS in pull-up e pull-down è la medesima. In figura 6, è mostrata la rete speculare di riporto.

|

| Figura 6: rete del riporto speculare. |

Nessun miglioramento dal punto di vista dell'occupazione d'area, ma miglioramento del tempo di propagazione del segnale all'uscita.

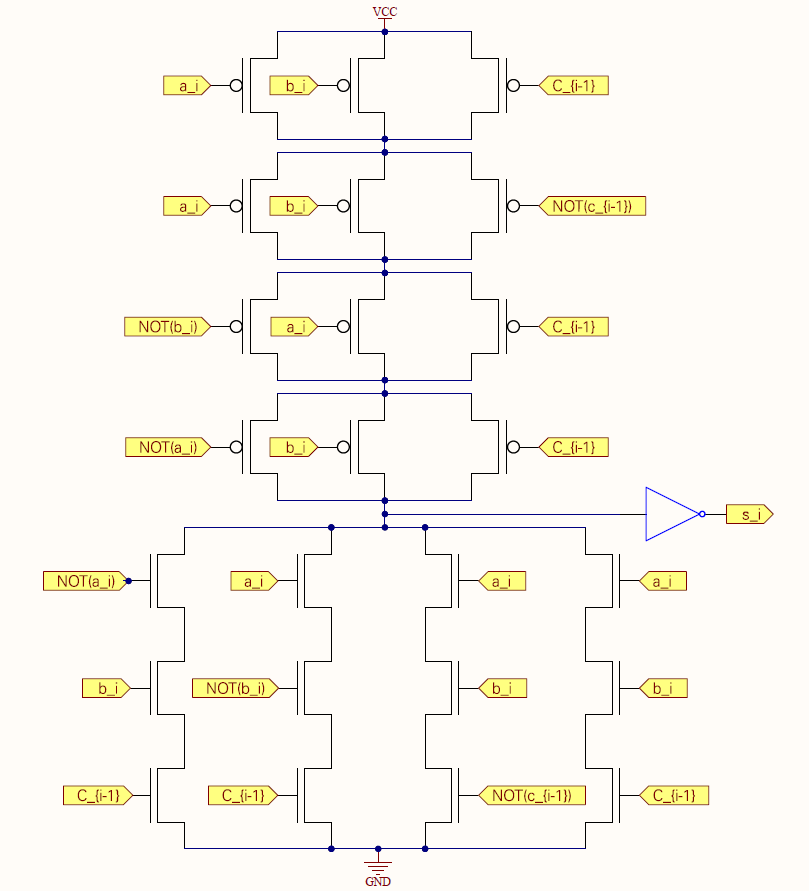

il risultato ottenuto da questo procedimento è che la somma può essere legata al riporto. Infatti,

Come nel caso precedente, il calcolo dei beta equivalenti.

La rete di pull-down porta a un caso peggiore quando sono accesi in serie ai e bi e ci-1. Essendo tre MOS in serie, il beta equivalente è: La rete di pull-up, invece, porta al caso peggiore quando sono accesi gli stessi ingressi. Tuttavia, si verifica un parallelo di tre MOS in serie al altri tre MOS. Il beta equivalente è:Potendo procedere come per il riporto, si crea anche per la somma una struttura CMOS speculare, in cui i pMOS hanno la stessa posizione degli nMOS.

|

| Figura 8: Full-Adder mirror. |

Si conclude che, sono necessari 10 MOS per il riporto, 14 MOS per la somma e 4 MOS per i due invertitori in uscita, per un totale di 28 MOS al Full-Adder.

Commenti

Posta un commento