Logica a pass-transistor - transmission gate(37)

La nuova famiglia logica dei pass-transistor è un'importante applicazione digitale dei transistori a effetto di campo. Un pass-transistor singolo ha l'obiettivo di riportare sull'uscita lo stesso valore presente sull'ingresso. Un esempio è rappresentato in figura 1.

|

| Figura 1: pass-transistor di tipo n (a sinistra) e di tipo p (a destra). |

Un transistore MOS, in circuiti digitali, ha la funzione di interruttore controllato da un segnale digitale, il quale può dunque assumere solo valore alto o valore basso. In particolare, il transistore nMOS può essere visto come un interruttore normalmente aperto (NO), che viene chiuso quando il segnale sul gate assume valore alto; al contrario, il transistore pMOS può essere visto come un interruttore normalmente chiuso (NC), che viene aperto nel momento in cui il segnale sul gate assume valore alto.

Allo stesso modo, il pass-transistor di tipo n (tipo p) acceso è come un interruttore chiuso (aperto) e consente il flusso della corrente. La capacità sull'uscita serve a mantenere il valore anche nel momento in cui si spegne il transistore.

La figura 2 mostra la tabella di funzionamento di un pass-transistor di tipo n. Si consideri il segnale al terminale di gate sempre a valore alto.

- Se l'uscita è identica all'ingresso, non avviene movimento di carica;

- Quando l'ingresso è al valore basso e l'uscita al valore alto, allora al momento dell'accensione del MOS deve avvenire un transitorio di scarica del condensatore (figura 2 percorso rosso). Il terminale d'uscita è il drain (è al potenziale maggiore) e l'ingresso il source (potenziale minore);

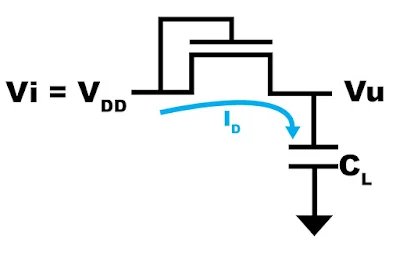

- al contrario, quando l'ingresso è al valore alto e l'uscita al valore basso, non appena il MOS viene acceso, si verifica un transitorio di carica del condensatore (figura 2 percorso azzurro). Il terminale a potenziale più alto è quello di ingresso, che assumerà la funzione di drain. Ovviamente, l'uscita è il source.

|

| figura 2: funzionamento di un pass- transistor di tipo n. |

|

| Figura 3: carica della capacità tramite pass-transistor. |

il risultato ottenuto afferma che il valore alto in uscita a un pass-transistor di tipo n è pari alla differenza tra alimentazione e soglia, detto anche 1 debole. Il valore basso è pari a zero, e si dice 0 forte.

Il caso del pMOS pass-transistor è leggermente differente. In figura 4 è mostrata la tabella di funzionamento. Si consideri il terminale di gate al valore basso.

|

| Figura 4: funzionamento del pass-transistor di tipo p. |

- Quando l'ingresso è al valore basso e l'uscita al valore alto, allora al momento dell'accensione del MOS deve avvenire un transitorio di scarica del condensatore (figura 4 in rosso). Il terminale di uscita è al potenziale maggiore (source del pMOS);

- Quando l'ingresso è al valore alto e l'uscita al valore basso, allora il procedimento è ora il transitorio di carica del condensatore (figura 4 in verde). Il terminale a potenziale maggiore sarà l'ingresso, che assume il ruolo del terminale di source.

Transmission gate

|

| Figura 5: circuito transmission gate. |

Il vantaggio del transmission gate, rispetto ai singoli pass-transistor, che si tratti di canale p o canale n, sta nella completa escursione al segnale di uscita: se l'ingresso è alto, anche l'uscita, all'accensione del transmission gate, raggiunge il valore alto pieno. Stesso ragionamento per il valore basso.

|

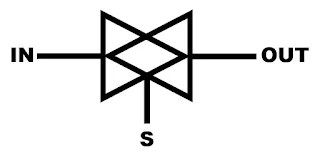

| Figura 6: simbolo del transmission gate. |

L'inserimento di un cerchio in corrispondenza del segnale di controllo S (figura 7) simboleggia la presenza di uno scambio di complementarietà: il segnale di controllo negato è collegato direttamente al gate del pass-transistor di tipo n. Il segnale non negato è collegato direttamente al pMOS.

|

| Figura 7: pass-transistor a segnale di controllo invertito. |

.png)

.png)

.png)

.png)

.png)

Commenti

Posta un commento