Tempo di propagazione di un invertitore CMOS (33)

Il transistore MOS, al pari del transistore bipolare a giunzione, non è un elemento perfettamente istantaneo, ma si compone anch'esso di capacità parassite che ne limitano le prestazioni in velocità. Questi effetti, infatti, sono visibili pienamente in fase di commutazione dell'uscita.

Nonostante la presenza di diverse capacità anomale, il circuito equivalente per l'invertitore CMOS con una capacità che rappresenti tutte le capacità interne è raffigurato in figura 1

|

| Figura 1: invertitore CMOS con capacità di carico. |

Il tempo di propagazione di questo circuito viene calcolato nel momento in cui l'uscita passa dal valore alto al valore basso, tenendo sempre presente che lo stesso tempo di propagazione viene valutato sul tempo impiegato dall'uscita a raggiungere il 50% dell'escursione:

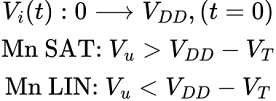

Per il calcolo di questo tempo, è necessario che il segnale in ingresso passi, nell’istante t=0, dal valore basso (0) al valore alto (VDD) e successivamente osservare come varia l’uscita e, di conseguenza, la regione di funzionamento dell'nMOS a pull-down.

Il tempo di propagazione totale si compone, quindi, di due tratti: il primo tratto comprende l’escursione dell’uscita dal valore alto alla differenza tra valore alto e tensione di soglia, nella quale il transistore lavora in regime di saturazione; il secondo tratto riguarda l'escursione tra valore differenza alto e soglia e il 50% del valore alto, nella quale il transistore lavora in regione lineare.

Il transistore pMOS a pull-up, per la tensione applicata tra source e gate, è spento. La legge al nodo Vu è la seguente:

- Calcolo del primo tratto: il transistore lavora in saturazione, la corrente di drain del transistore nMOS non dipende in alcun modo dalla tensione di uscita. L'espressione che si ottiene è la seguente:

- Calcolo del secondo tratto: dall'istante appena calcolato, il transistore lavora in regime lineare. La corrente diventa

svolgendo il calcolo all'interno dell'integrale, si ottiene quindiche è la formula del tempo di propagazione totale per l'escursione del segnale da alto a basso.

|

| Figura 2: andamento dell'uscita in un invertitore CMOS |

A partire dall'ipotesi secondo cui la tensione di alimentazione ha un valore maggiore rispetto alla tensione di soglia del MOS, si può ottenere una semplice formula approssimata del tempo di propagazione:essendo il logaritmo naturale di 3 approssimabile a 1, il valore approssimato del tempo di propagazione è:la formula è molto più pratica per il calcolo della suddetta grandezza in tutte le applicazioni digitali di un invertitore CMOS o una qualsiasi porta logica realizzata in CMOS, essendo che tramite la combinazione in serie o in parallelo di MOS è possibile ridurre ogni porta a un singolo invertitore CMOS.

.png)

.png)

.png)

.png)

.png)

Commenti

Posta un commento